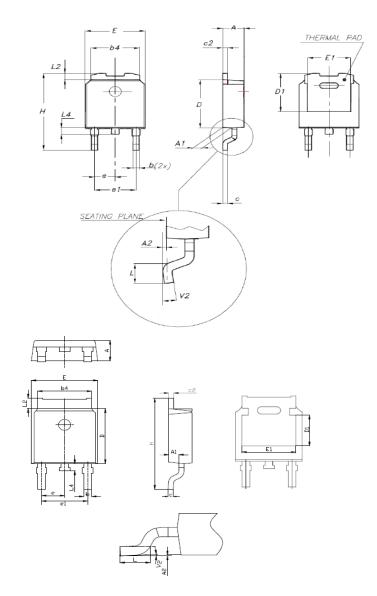

# DPAK Comparison ST STD die pad VS TFME LARGE die pad

**Involved Products:**

GD5NB120SZ(607B), STGD5NB120SZT4

|            | 1    | TYPE "A | ,,,  | Т     | YPE "C | 2"    |

|------------|------|---------|------|-------|--------|-------|

|            |      | STD-ST  | 1    | LA    | RGE-TF | ME    |

| DIM. mm    |      | mm      |      | mm    |        |       |

| DIM.       | MIN  | TYP     | MAX  | MIN   | TYP    | MAX   |

| A          | 2.2  |         | 2.4  | 2.2   | 2.3    | 2.38  |

| A1         | 0.9  |         | 1.1  | 0.9   | 1.01   | 1.1   |

| <b>A2</b>  | 0.03 |         | 0.23 | 0     |        | 0.1   |

| b          | 0.64 |         | 0.9  | 0.72  |        | 0.85  |

| b4         | 5.2  |         | 5.4  | 5.13  | 5.33   | 5.46  |

| С          | 0.45 |         | 0.6  | 0.47  |        | 0.6   |

| c2         | 0.48 |         | 0.6  | 0.47  |        | 0.6   |

| D          | 6    |         | 6.2  | 6     | 6.1    | 6.2   |

| D1         | 4.95 | 5.1     | 5.25 | 5.1   |        | 5.6   |

| E          | 6.4  |         | 6.6  | 6.5   | 6.6    | 6.7   |

| <b>E</b> 1 | 4.6  | 4.7     | 4.8  | 5.2   |        | 5.5   |

| e          | 2.16 | 2.28    | 2.4  | 2.186 | 2.286  | 2.386 |

| e1         | 4.4  |         | 4.6  |       |        |       |

| Н          | 9.35 |         | 10.1 | 9.8   | 10.1   | 10.4  |

| L          | 1    |         | 1.5  | 1.4   | 1.5    | 1.7   |

| (L1)       | 2.6  | 2.8     | 3    |       | 2.9    |       |

| L2         | 0.65 | 0.8     | 0.95 | 0.9   |        | 1.25  |

| L3         |      |         |      |       | 0.51   |       |

| L4         | 0.6  |         | 1    | 0.6   | 0.8    | 1     |

| L6         |      |         |      |       | 1.80   |       |

| Θ1         |      |         |      | 5°    | 7°     | 9°    |

| Θ 2        |      |         |      | 5°    | 7°     | 9°    |

| R          |      | 0.2     |      |       |        |       |

| V2         | O°   |         | Q٥   | O°    |        | Q٥    |

ST

**TFME**

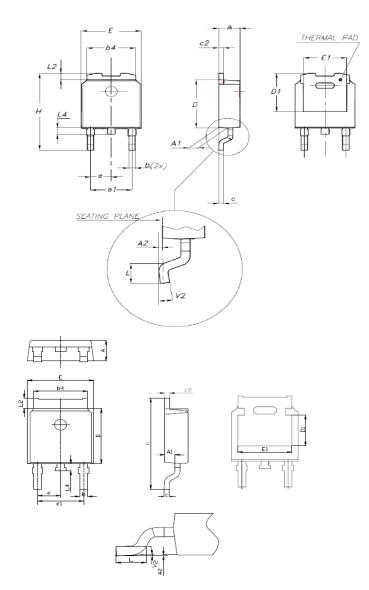

# DPAK Comparison ST LARGE die pad VS TFME LARGE die pad

#### **Involved Products:**

STGD10NC60HDT4, STGD10NC60HT4, STGD14NC60KT4, STGD4M65DF2 STGD5H60DF, STGD5H60DFSF, STGD6M65DF2, STGD6NC60HDT4 STGD7NB60ST4, STGD7NC60HT4

| <b>TYPE "A2"</b> |      |      |            | TYPE "C2" |       |       |

|------------------|------|------|------------|-----------|-------|-------|

| LARGE-ST         |      |      | LARGE-TFME |           |       |       |

| DIM.             | mm   |      |            |           | mm    |       |

| DIM.             | MIN  | TYP  | MAX        | MIN       | TYP   | MAX   |

| A                | 2.2  |      | 2.4        | 2.2       | 2.3   | 2.38  |

| A1               | 0.9  |      | 1.1        | 0.9       | 1.01  | 1.1   |

| <b>A2</b>        | 0.03 |      | 0.23       | 0         |       | 0.1   |

| b                | 0.64 |      | 0.9        | 0.72      |       | 0.85  |

| <b>b4</b>        | 5.2  |      | 5.4        | 5.13      | 5.33  | 5.46  |

| С                | 0.45 |      | 0.6        | 0.47      |       | 0.6   |

| c2               | 0.48 |      | 0.6        | 0.47      |       | 0.6   |

| D                | 6    |      | 6.2        | 6         | 6.1   | 6.2   |

| D1               | 4.95 | 5.1  | 5.25       | 5.1       |       | 5.6   |

| E                | 6.4  |      | 6.6        | 6.5       | 6.6   | 6.7   |

| E1               | 5.1  | 5.2  | 5.3        | 5.2       |       | 5.5   |

| e                | 2.16 | 2.28 | 2.4        | 2.186     | 2.286 | 2.386 |

| e1               | 4.4  |      | 4.6        |           |       |       |

| Н                | 9.35 |      | 10.1       | 9.8       | 10.1  | 10.4  |

| L                | 1    |      | 1.5        | 1.4       | 1.5   | 1.7   |

| (L1)             | 2.6  | 2.8  | 3          |           | 2.9   |       |

| L2               | 0.65 | 0.8  | 0.95       | 0.9       |       | 1.25  |

| L3               |      |      |            |           | 0.51  |       |

| L4               | 0.6  |      | 1          | 0.6       | 0.8   | 1     |

| L6               |      |      |            |           | 1.80  |       |

| Θ1               |      |      |            | 5°        | 7°    | 9°    |

| Θ2               |      |      |            | 5°        | 7°    | 9°    |

| R                |      | 0.2  |            |           |       |       |

| V2.              | 0°   |      | 8°         | 0°        |       | 8°    |

ST

**TFME**

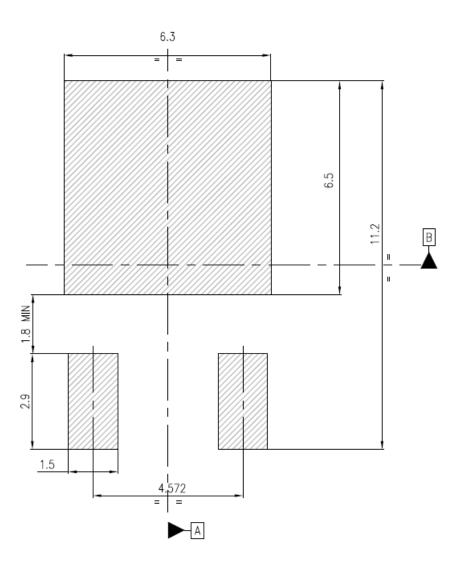

# **DPAK Unchanged Recommended Footprint**

Dear Customer,

Continuing in the aim of a constant process improvement, please be informed that we're going to use DPAK Automatic Assembly/Testing for Selected IGBTs in Tongfu Microelectronics (China). DPAK products, manufactured in Tongfu Microelectronics (China), guarantee the same quality and electrical characteristics as reported in the relevant data sheets. Devices used for qualification are available as samples.

The involved product series and affected packages are listed in the attached file.

Any other Product related to the above series, manufactured in Tongfu Microelectronics (China), even if not expressly included or partially mentioned in the attached table, is affected by this change.

#### Qualification program and results availability:

The reliability test report plan is provided in attachment to this document.

#### Samples availability:

Samples of the test vehicle devices will be available on request starting from week 48-2017. Any other sample request will be processed and scheduled by Power Transistor Division upon request.

| Product Family Description | Package | Part Number - Test Vehicle |

|----------------------------|---------|----------------------------|

|                            |         | STGD5H60DFSF               |

| IGBT                       | DPAK    | STGD6NC60HDT4              |

|                            |         | STGD7NC60HT4               |

#### **Change implementation schedule:**

The production start and first shipments will be implemented according to our work in progress and materials availability:

| Product Family | 1 <sup>st</sup> Shipments |

|----------------|---------------------------|

| IGBT           | From Week 10-2018 *       |

<sup>\*</sup> Due to the current long delivery time, we need to speed-up PCN approval.

Lack of acknowledgement of the PCN within 30 days will constitute acceptance of the change. After acknowledgement, lack of additional response within the 90 days period will constitute acceptance of the change (Jedec Standard No. 46-C). In any case, first shipment may start earlier with customer written agreement.

# Marking and traceability:

Unless otherwise stated by customer specific requirement, traceability of IGBTs manufactured in Tongfu Microelectronics (China) subcontractor will be ensured by "GF" as first digits of the trace code, internal code (Finished Good) and Q.A. number.

Sincerely Yours.

# **Reliability Report Plan**

DPAK IGBT and IGBT+Diode Assembly Capacity

Expansion

in Tongfu Microelectronics (China)

INDUSTRIAL

**General Information**

Product Lines: IGBT El6201 - Diode F62B

IGBT IV6201 - Diode F62I

**IGBT IV6401**

P/N: STGD5H60DFSF

STGD6NC60HDT4 STGD7NC60HT4

Product Group: ADG

**Product division:** Power Transistor Division

Package: DPAK

Silicon Process techn.: IGBT Planar

**IGBT Trench**

Locations

Wafer Fab and EWS IGBT: Catania (Italy)

Plant: Diode:Tours (France)

Assembly and Tongfu Microelectronics

testing plant: (China)

Reliability Lab: ADG - Catania Reliability Lab.

#### **DOCUMENT INFORMATION**

| Version | Date          | Pages | Prepared by                     | Approved by | Comment     |

|---------|---------------|-------|---------------------------------|-------------|-------------|

| 1.0     | November 2017 | 8     | <ul><li>A. Settinieri</li></ul> | C. Cappello | First issue |

Note: This report is a summary of the reliability trials performed in good faith by STMicroelectronics in order to evaluate the potential reliability risks during the product life using a set of defined test methods.

This report does not imply for STMicroelectronics expressly or implicitly any contractual obligations other than as set forth in STMicroelectronics general terms and conditions of Sale. This report and its contents shall not be disclosed to a third party without previous written agreement from STMicroelectronics.

# ADG (Automotive & Discrete Group) Quality and Reliability Reliability Power Transistor - CATANIA

Rel 07-17

#### **TABLE OF CONTENTS**

| 1 | APPLICABLE AND REFERENCE DOCUMENTS | 3 |

|---|------------------------------------|---|

| 2 | GLOSSARY                           | 3 |

|   | RELIABILITY EVALUATION OVERVIEW    |   |

| _ | 3.1 OBJECTIVES                     |   |

|   | 3.2 CONCLUSION                     |   |

| 4 | DEVICE CHARACTERISTICS             | 4 |

|   | 4.1 DEVICE DESCRIPTION             | 4 |

|   | 4.2 Construction note              | 4 |

| 5 | TESTS RESULTS SUMMARY              | 5 |

|   | 5.1 Test vehicles                  |   |

|   | 5.2 RELIABILITY TEST PLAN SUMMARY  |   |

| 6 | ANNEXES 6.0                        | 7 |

|   | 6.1Tests Description               | 7 |

#### 1 APPLICABLE AND REFERENCE DOCUMENTS

| Document reference | Short description                                       |

|--------------------|---------------------------------------------------------|

| JESD47             | Stress-Test-Driven Qualification of Integrated Circuits |

|                    |                                                         |

#### **2 GLOSSARY**

| DUT | Device Under Test |

|-----|-------------------|

| SS  | Sample Size       |

| HF  | Halogen Free      |

#### **3 RELIABILITY EVALUATION OVERVIEW**

#### 3.1 Objectives

To qualify DPAK IGBT and IGBT+Diode assembled in TONGFU Microelectronics (China)

#### 3.2 Conclusion

Qualification Plan requirements have been fulfilled without exception. Reliability tests have shown that the devices behave correctly against environmental tests (no failure). Moreover, the stability of electrical parameters during the accelerated tests demonstrates the ruggedness of the products and safe operation, which is consequently expected during their lifetime.

**PACKAGE: DPAK**

**PACKAGE: DPAK**

### **4 DEVICE CHARACTERISTICS**

#### 4.1 **Device description**

IGBT Planar / IGBT Trench

### 4.2 Construction note

#### D.U.T.: STGD5H60DFSF

| Wafer/Die Information   |                                                                        |  |  |

|-------------------------|------------------------------------------------------------------------|--|--|

| Technology              | IGBT Trench - Diode                                                    |  |  |

| Wafer Fab               | IGBT Catania (Italy) - Diode Tours (France)                            |  |  |

| Die finishing back side | IGBT AI/Ti/NiV/Ag                                                      |  |  |

| Die size                | IGBT: 2510 x 1950 μm <sup>2</sup> / Diode: 1100 x 1100 μm <sup>2</sup> |  |  |

| Metal                   | IGBT AICu                                                              |  |  |

| Passivation type        | GBT SiN (nitride)                                                      |  |  |

| Assembly/Testing information        |                                      |  |  |

|-------------------------------------|--------------------------------------|--|--|

| Assembly site                       | Tongfu Microelectronics (China)      |  |  |

| Package description                 | DPAK                                 |  |  |

| Molding compound                    | HF Epoxy Resin                       |  |  |

| Frame material                      | Raw Copper                           |  |  |

| Die attach material                 | Soft Solder UMICORE Pb/Sn/Ag         |  |  |

| Wire bonding process                | Ultra Thermosonic                    |  |  |

| Wires bonding materials             | Gate: Al (5mils) Source: Al (15mils) |  |  |

| Lead finishing/bump solder material | Pure Tin                             |  |  |

#### D.U.T.: STGD6NC60HDT4

| Wafer/Die Information   |                                                                       |  |  |

|-------------------------|-----------------------------------------------------------------------|--|--|

| Technology              | IGBT Planar - Diode                                                   |  |  |

| Wafer Fab               | IGBT Catania (Italy) - Diode Tours (France)                           |  |  |

| Die finishing back side | IGBT Cr/Ni/Ag                                                         |  |  |

| Die size                | IGBT 1690 x 2620 μm <sup>2</sup> / Diode: 1100 x 1100 μm <sup>2</sup> |  |  |

| Metal                   | IGBT AISi                                                             |  |  |

| Passivation type        | IGBT SiN (nitride)                                                    |  |  |

| Assembly/Testing information        |                                     |  |  |

|-------------------------------------|-------------------------------------|--|--|

| Assembly site                       | Tongfu Microelectronics (China)     |  |  |

| Package description                 | DPAK                                |  |  |

| Molding compound                    | HF Epoxy Resin                      |  |  |

| Frame material                      | Raw Copper                          |  |  |

| Die attach material                 | Soft Solder UMICORE Pb/Sn/Ag        |  |  |

| Wire bonding process                | Ultra Thermosonic                   |  |  |

| Wires bonding materials             | Gate: Al (5mils) Source: Al (5mils) |  |  |

| Lead finishing/bump solder material | Pure Tin                            |  |  |

**PACKAGE: DPAK**

#### D.U.T.: STGD7NC60HT4

| Wafer/Die Information   |                                  |  |  |  |  |

|-------------------------|----------------------------------|--|--|--|--|

| Technology              | IGBT Planar                      |  |  |  |  |

| Wafer Fab               | IGBT Catania (Italy)             |  |  |  |  |

| Die finishing back side | IGBT Cr/Ni/Ag                    |  |  |  |  |

| Die size                | IGBT 3500 x 2880 μm <sup>2</sup> |  |  |  |  |

| Metal                   | IGBT AISi                        |  |  |  |  |

| Passivation type        | IGBT SiN (nitride)               |  |  |  |  |

| Assembly/Testing information        |                                      |  |  |  |

|-------------------------------------|--------------------------------------|--|--|--|

| Assembly site                       | Tongfu Microelectronics (China)      |  |  |  |

| Package description                 | DPAK                                 |  |  |  |

| Molding compound                    | HF Epoxy Resin                       |  |  |  |

| Frame material                      | Raw Copper                           |  |  |  |

| Die attach material                 | Soft Solder UMICORE Pb/Sn/Ag         |  |  |  |

| Wire bonding process                | Ultra Thermosonic                    |  |  |  |

| Wires bonding materials             | Gate: Al (5mils) Source: Al (10mils) |  |  |  |

| Lead finishing/bump solder material | Pure Tin                             |  |  |  |

#### **5 TESTS RESULTS SUMMARY**

# 5.1 **Test vehicles**

| Lot | Part Number   | Silicon Lines | Package | Wafer Fab | Assy Plant       | Comments |

|-----|---------------|---------------|---------|-----------|------------------|----------|

| 1   | STGD5H60DFSF  | EI62          |         | 0         | Tongfu           |          |

| 2   | STGD6NC60HDT4 | IV62          | DPAK    | Catania   | Microelectronics |          |

| 3   | STGD7NC60HT4  | IV64          |         | (Italy)   | (China)          |          |

# 5.2 Reliability test plan summary

| #    | Stress               | P   | Std ref.           | Conditions                                                                                   | Sample Size Steps                                     |       | Failure/SS |         |         |  |

|------|----------------------|-----|--------------------|----------------------------------------------------------------------------------------------|-------------------------------------------------------|-------|------------|---------|---------|--|

|      | (Abrv)               | С   |                    |                                                                                              | (S.S.)                                                |       | Lot 1      | Lot 2   | Lot 3   |  |

| 1    | TEST                 |     | User specification | All qualification parts tested per the requirements of the appropriate device specification. |                                                       |       | 0/190      | 0/190   | 0/190   |  |

| 2    | External visual      |     | JESD22<br>B-101    | All devices submitted for testing                                                            |                                                       | 0/190 | 0/190      | 0/190   |         |  |

| Sili | con Oriented T       | est |                    |                                                                                              |                                                       |       |            |         |         |  |

| 3    | HTRB                 | N   | JESD22<br>A-108    | Tj = 150°C ; BIAS = 480V                                                                     | 45 x lot                                              | 1000H | 04/2018    | 04/2018 | 04/2018 |  |

| 4    | HTGB                 | Ζ   | JESD22<br>A-108    | Tj=150°C ; BIAS= 25V                                                                         | 45 x lot                                              | 1000H | 04/2018    | 04/2018 | 04/2018 |  |

| Pac  | kage Oriented        | Te  | st                 |                                                                                              |                                                       |       |            |         |         |  |

| 5    | Pre-<br>conditioning |     | JESD22<br>A-113    | Dryng 24H @ 125°C<br>Store 168H @ TA=85°C<br>RH=85% IR Reflow @ 260°C<br>3 times             | All devices to<br>be subjected<br>to H3TRB,<br>TC, AC | Final | 04/2018    | 04/2018 | 04/2018 |  |

| 6    | тс                   | Υ   | JESD22<br>A-104    | TA=-65°C TO 150°C<br>1 HOURS / CYCLE                                                         | 25 x lot                                              | 500cy | 04/2018    | 04/2018 | 04/2018 |  |

| 7    | AC                   | Υ   | JESD22<br>A-102    | TA=121°C; PA=2ATM                                                                            | 25 x lot                                              | 96H   | 04/2018    | 04/2018 | 04/2018 |  |

# ADG (Automotive & Discrete Group) Quality and Reliability Reliability Power Transistor - CATANIA

Rel 07-17

|          |               |          | IEODOO                             | TA 0500 DIL 050/ |             |        |         |         |         |

|----------|---------------|----------|------------------------------------|------------------|-------------|--------|---------|---------|---------|

| 8        | H3TRB         | Υ        | JESD22                             | TA=85°C ; RH=85% | 25 x lot    | 1000H  | 04/2018 | 04/2018 | 04/2018 |

| ١        | HOTE          |          | A-101                              | BIAS=80V         | 20 X 10t    | 100011 | 04/2010 | 04/2010 | 04/2010 |

| 9        | IOL           | N        | MIL-STD-750                        | AT: >105°C       | 25 x lot    | 10Kcv  | 04/2018 | 04/2018 | 04/2018 |

| 9        | IOL           | IN       | Method 1037                        | ΔTj ≥105°C       | 25 X 10t    | TUNCY  | 04/2016 | 04/2016 | 04/2016 |

|          |               |          | ESDA-                              |                  |             |        |         |         |         |

|          |               |          | JEDEC_ JES-                        | CDM / HBM        | 3 x lot     |        |         | 04/2018 | 04/2018 |

| 10       | ESD           |          | 001                                |                  |             |        | 04/2018 |         |         |

|          |               |          | ANSI-ESD                           |                  |             |        |         |         |         |

|          |               |          | S5.3.1                             |                  |             |        |         |         |         |

|          | Physical      |          | JESD22                             |                  | 00 1-1      |        | 0/00    | 0/00    | 0/00    |

| 11       | Dimension     |          | B-100                              |                  | 30 x lot    |        | 0/30    | 0/30    | 0/30    |

| 12       | Solderability |          | J-STD-002                          |                  | 10 x lot    |        | 0/10    | 0/10    | 0/10    |

| 13       | Terminal      |          | MIL-STD-750                        |                  | 20          |        | 0/30    | 0/30    | 0/30    |

| 13       | Strength      |          | Method 2036                        |                  | 30          |        | 0/30    | 0/30    | 0/30    |

|          |               |          | IECDOO                             |                  | 10 bonds    |        |         |         |         |

| 14       | Bond Shear    | nd Shear | from min of                        |                  | 0/5         | 0/5    | 0/5     |         |         |

|          |               |          | B-116                              |                  | 5 devices   |        |         |         |         |

|          | Resistance    |          |                                    |                  |             |        |         |         |         |

| 15       |               |          |                                    |                  | 12          |        | 0/12    | 0/12    | 0/12    |

|          |               |          | A-111                              |                  |             |        | 5,12    | J, 12   | 5,12    |

| 14<br>15 | Resistance    |          | JESD22<br>B-116<br>JESD22<br>A-111 |                  | from min of |        | 0/5     | 0/5     |         |

# **<u>6</u> ANNEXES 6.0**

# **6.1Tests Description**

| Test name                                                                            | Description                                                                                                                                                                                                                      | Purpose                                                                                                                                                                                                                                                                                                                               |  |  |  |

|--------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| HTRB High Temperature Reverse Bias  HTGB / HTFB High Temperature Forward (Gate) Bias | The device is stressed in static configuration, trying to satisfy as much as possible the following conditions: low power dissipation; max. supply voltage compatible with diffusion process and internal circuitry limitations; | accelerated way.  To maximize the electrical field across either                                                                                                                                                                                                                                                                      |  |  |  |

| Package Oriented                                                                     |                                                                                                                                                                                                                                  |                                                                                                                                                                                                                                                                                                                                       |  |  |  |

| <b>PC</b> Preconditioning                                                            | The device is submitted to a typical temperature profile used for surface mounting devices, after a controlled moisture absorption.                                                                                              | As stand-alone test: to investigate the moisture sensitivity level. As preconditioning before other reliability tests: to verify that the surface mounting stress does not impact on the subsequent reliability performance. The typical failure modes are "pop corn" effect and delamination.                                        |  |  |  |

| AC<br>Auto Clave<br>(Pressure Pot)                                                   | The device is stored in saturated steam, at fixed and controlled conditions of pressure and temperature.                                                                                                                         | To investigate corrosion phenomena affecting die or package materials, related to chemical contamination and package hermeticity.                                                                                                                                                                                                     |  |  |  |

| TC<br>Temperature<br>Cycling                                                         | The device is submitted to cycled temperature excursions, between a hot and a cold chamber in air atmosphere.                                                                                                                    | To investigate failure modes related to the thermo-mechanical stress induced by the different thermal expansion of the materials interacting in the die-package system. Typical failure modes are linked to metal displacement, dielectric cracking, molding compound delamination, wire-bonds failure, die-attach layer degradation. |  |  |  |

| IOL / TF Intermittent Operating Life                                                 | The device is submitted to cycled temperature excursions generated by power cycles (ON/OFF) at T ambient.                                                                                                                        | To investigate failure modes related to the thermo-mechanical stress induced by the different thermal expansion of the materials interacting in the die-package system. Typical failure modes are linked to metal displacement, dielectric cracking, molding compound delamination, wire-bonds failure, die-attach layer degradation. |  |  |  |

| H3TRB/THB<br>Temperature<br>Humidity Bias                                            | The device is biased in static configuration minimizing its internal power dissipation, and stored at controlled conditions of ambient temperature and relative humidity.                                                        | To evaluate the package moisture resistance with electrical field applied, both electrolytic and galvanic corrosion are put in evidence.                                                                                                                                                                                              |  |  |  |